- Top Results

- Bosch Sensortec Community

- Learn

- Knowledge base

- BMI160 FIFO Advanced Usage

BMI160 FIFO Advanced Usage

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

FIFO description

The BMI160 integrates a 1024-bytes data FIFO. The FIFO contains frames of data, and each frame contains only one sample per sensor. Each sensor element can be enabled for the FIFO individually. The data frames can be configured into different formats as shown in Figure 1. If each sensor is with different ODRs, then each frame contains samples from different subsets of sensors which are enabled for the FIFO. In that case, the size of frames is not constant.

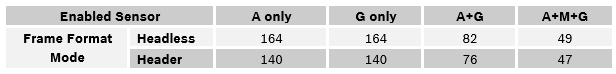

The maximum number of frames in the FIFO is determined by different configurations. Assuming that all the sensors are with the same ODR, the following table demonstrates the maximum frames of sensor data can be stored in the FIFO for different frame format modes:

Table 1: Maximum number of frames in FIFO

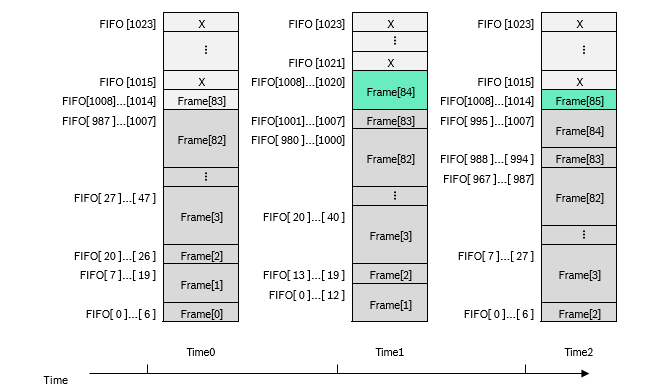

The FIFO operates in a mode that collects data constantly. When the FIFO buffer is full, the data collection continues and the oldest entry is discarded. For the example in Figure 2, at the moment Time0, FIFO buffer has room for 9 bytes. So the next frame that contains 13 bytes does not fit in the FIFO. Therefore, at Time1, the oldest frame Frame[0] in FIFO[0…6] is discarded, the remaining frames are shifted down and the new frame Frames[84] is pushed into FIFO[1008…1020]. At Time2, when the new frame is ready, the oldest frame continues to be discarded.

Figure 2: FIFO full representation, the Oldest Frames are discarded

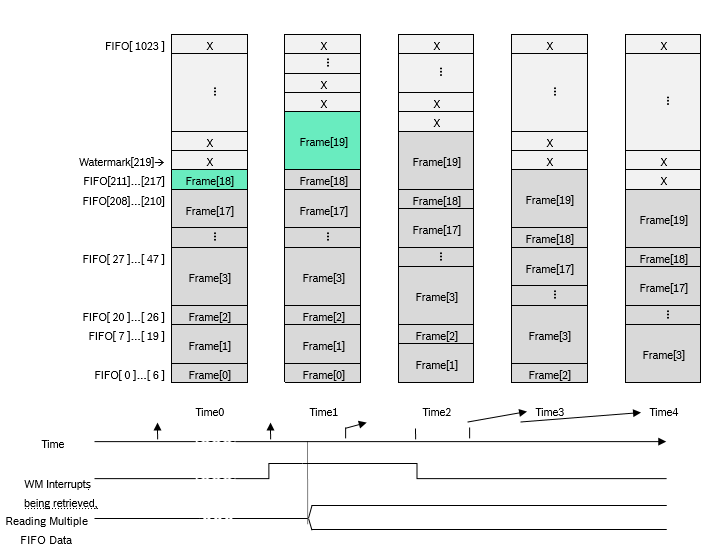

When data is being read, data collection continues. An example is shown in Figure 3. At Time0, the new frame Frame[19] is pushed into FIFO and the watermark interrupt is triggered. Then after some delay, the interrupt is serviced and a burst read of FIFO begins. In order to read out all the valid data in FIFO and generate a timestamp in Header mode, the length of the burst read is set to the watermark level plus two maximum-sized frames plus four bytes. At Time2, as the burst read takes longer than the sensor data is generated, a new frame Frame[20] is added into FIFO. At Time3, all the valid data including Frame[20] is read out and a Sensortime frame is returned.

The example below describes the steps of FIFO setting and FIFO data retrieval. After sensor configuration, Accel and Gyro are set to Normal mode. Then FIFO is configured to store Accel and Gyro data in Header mode. By burst reading FIFO data Register 0x24, data is read from FIFO every 50ms.

Figure 4: Steps to enable FIFO and retrieve FIFO data every 50ms

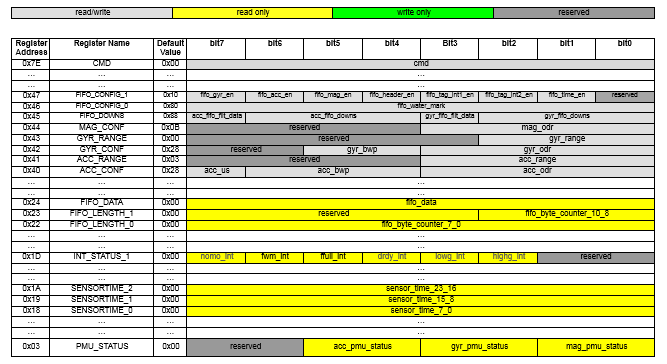

FIFO register

In the following table, the most important registers for FIFO configuration and usage (as excerpt of the full register map in Datasheet Section 2.11) are shown.

Table 2: Important registers for FIFO usage

FIFO configuration registers (0x46-0x47)

FIFO configuration registers can be used to:

- read or set the current FIFO watermark level

- set different modes of operation of the FIFO, i.e. which data will be stored in it and which format will be used (header or headerless mode).

fifo_water_mark

fifo_water_mark defines the FIFO watermark level. An interrupt will be generated when the number of entries in the FIFO exceeds fifo_water_mark.

Note:

The unit of fifo_water_mark is 4 bytes.

fifo_acc_en,fifo_gyr_en,fifo_mag_en

fifo_xxx(acc, gyr, mag)_en defines if the xxx data is stored in FIFO. If fifo_xxx_en = 0, no data is stored in FIFO; if fifo_xxx_en = 1, xxx data is stored in FIFO (for all three axes). When all fifo_xxx_en are ‘0’, the FIFO is disabled, no sensor data is stored in FIFO and no headers are written.

fifo_header_en

fifo_header_en defines the FIFO frame mode as discussed in Chapter 4. If fifo_header_en = 1, FIFO is in Header mode, each frame contains a header and data; If fifo_header_en = 0, FIFO is in Headerless mode, each frame contains data only.

For Header mode, the output data rates of all enabled sensors for the FIFO can be different.

However, for Headerless mode, the output data rates of all enabled sensors for the FIFO should be identical. If the output data rates are different in Headerless mode, the FIFO waits until the data with the lowest output data rate is ready and then stores the frame as shown in Figure 5.

Figure 5: FIFO frame modes behave differently with not identical ODR for sensors

For example, when Accel is set to 100Hz and Gyro is set to 200Hz, the frame of data is generated at 200Hz in Header mode and at 100Hz in Headerless mode.

For further discussion about FIFO frame modes, see Chapter 4.

fifo_tag_int1_en, fifo_tag_int2_en

fifo_tag_int1_en and fifo_tag_int2_en define if the FIFO tags the voltage on interrupt pin 1 or 2 in the FIFO header. To enable this function, int1_input_en and/or int2_input_en should be set to ‘1’ in Register (0x54) INT_LATCH.

fifo_time_en

fifo_time_en defines if sensortime frame in FIFO is enabled. When fifo_time_en = 0, no sensortime frame will be returned. When fifo_time_en = 1, a sensortime frame will be returned after the last valid frame when the number of data that are read is greater than that of valid frames in the FIFO. When reading from FIFO with burst read, the AP/MCU should read more than the bytes (FIFO byte counter + 4 bytes). These four bytes contain one frame header that indicates the Sensortime frame and 3 bytes for the real sensor time. FIFO data register (0x24)

When reading out data from FIFO, read burst access must be used. The address does not increment when the read burst reads at the address of FIFO_DATA. When a frame is only partially read out, it is retransmitted including the header at the next readout. The data format depends on the setting of FIFO Configuration Registers (0x46-0x47). The FIFO data is organized by frame, as described in Chapter 4.

FIFO length registers (0x22-0x23)

FIFO length registers contain a FIFO byte counter. It represents the current fill level of the FIFO buffer. This includes the Skip frame for a full FIFO. An empty FIFO corresponds to 0x000. The byte counter can be reset by reading out all frames from the FIFO buffer or when the FIFO is reset through the Register (0x7E) CMD. The byte counter is updated when a complete frame is read or written.

FIFO downsampling register (0x45)

The register (0x45) FIFO_DOWN provides xxx_fifo_filt_data and xxx_fifo_downs. Using these bits, the data stored in FIFO is downsampled compared to the ODR settings.

If xxx_fifo_filt_data = 0, unfiltered data will be selected as the data source for FIFO downsampling(1600Hz for Accel and 6400Hz for gyro).

If xxx_fifo_filt_data = 1, filtered data will be used as the data source for FIFO downsampling. This is identical to the ODR setting. Then the data stored in FIFO is related to the ODR and xxx_fifo_downs. For example, xxx_fifo_downs = 2, then every 4 samples output from data registers (updated based on ODR settings) will be stored in FIFO.

FIFO interrupt

The FIFO full interrupt and the watermark interrupt can be enabled/disabled through the Register (0x51) INT_EN_1 and can be mapped/unmapped to interrupt pin 1 or 2 through the Register (0x56) INT_MAP_1. Detailed information can be found in BMI160 Datasheet.

When FIFO is full, the FIFO full interrupt is issued and the next full data sample will cause FIFO overflow, which may cause samples to be deleted. Technically, this means that the FIFO full interrupt is issued whenever the remaining space in the FIFO is less than two maximum-sized frames.

The FIFO watermark interrupt is fired when the FIFO fill level in fifo_byte_counter in Register (0x22-0x23) FIFO_LENGTH is above the pre-configured watermark defined in fifo_watermark in Register (0x46-0x47) FIFO_CONFIG.

FIFO flush function

In order to empty the FIFO content, the user should write the command word 0xB0 into the command register 0x7E.

Note:

This action only clears the data content of FIFO and it does not change any FIFO configuration.

FIFO related error code

In the Error register, there are two FIFO related error code fields as follows:

0x0110: ODRs of enabled sensors in headless mode do not match, which means when headless mode is enabled for more than one sensor, these sensors are not set to the same ODR.

0x0111: unfiltered data is used in low power mode, which means in low power mode, only filtered data can be selected to fill FIFO. Because there is no real unfiltered data in low power mode, the sensor only gets the data based on the defined time interval.

FIFO frame

The BMI160 provides two different modes: headerless mode and header mode, as described in Chapter 3.They are detailed in following chapters.

Header mode

When FIFO is set to “header mode“, the data byte format differs depending on the type of frame. There are two basic frame types, i.e. control frame and regular data frame. Each different type of control frame has its own data byte format. It can contain skipped frames, sensortime data or FIFO configuration information, as described in BMI160 Datasheet. If the frame type is a regular frame (sensor data), the data byte section of the frame depends on how the data is being transmitted in this frame (as specified in the header byte section). It can include data from a single sensor or any combination of accelerometer, gyroscope and external sensor data. The following formula calculates the average size of the frame in Header mode:

Frame_SizeAVG = (Max(Aodr,Godr,Modr)*1+6*Aodr+6*Godr+8*Modr)/Max(Aodr,Godr,Modr) byte (1)

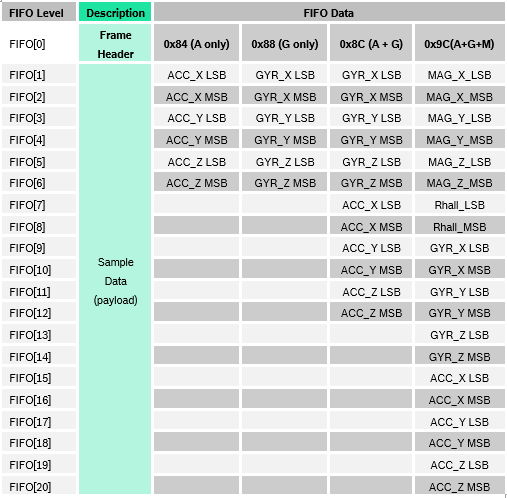

The data stored in FIFO uses the following format in header mode:

Table 3: Parts of FIFO data format in header mode

Note:

The above regular frame header contains the tags of interrupts in the last two bits fh_ext<1:0>. When fifo_tag_int1_en or fifo_tag_int2_en is enabled, the regular frame header may change. Take Accel only as an example, fifo_tag_int1_en and int1_input_en are enabled. If the Accel data is stored in FIFO while the interrupt pin 1 is high, the regular frame header is 0x85 instead of 0x84.

There are other FIFO frame headers:

- 0x48: CFG frame, which indicates the range or other configuration changes of A, G and M during FIFO storing.

- 0x40: Skip frame, which indicates how many frames are skipped when FIFO is full. If more than 255 frames are skipped, 255 is returned as the number of skipped frames.

- 0x44: Sensortime frame. The data byte part of a Sensortime frame consists of 3 bytes and contains a 24-bit sensortime. The Sensortime frame does not consume memory in FIFO.

- 0x80: Overread frame. The data byte part of an Overread frame consists of a redundant byte 0x00.

Detailed information on FIFO frame header format can be found in BMI160 Datasheet.

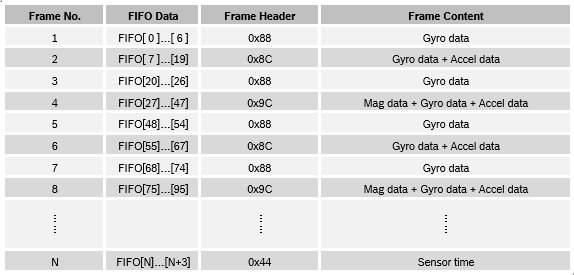

Example: how data stores in FIFO in Header mode

- Write 0x11, 0x15 into CMD register 0x7E in sequence to set A, G into normal power mode.

- Write 0x28 into register ACC_CONF (0x40) to set acceleration data rate to 100Hz.

- Write 0x29 into register GYR_CONF (0x42) to set gyro data rate to 200Hz.

- Enable and configure M via secondary interface according to AN First steps with the BMI160, set the magnetic data rate to 50Hz.

- Write 0xF2 into register FIFO_CONFIG_1 (0x47) to enable A, G and M data stored in FIFO. Also enable the header and timestamp for the FIFO.

Then FIFO works and stores data in the following format:

Table 4: FIFO data in header mode

Headerless mode

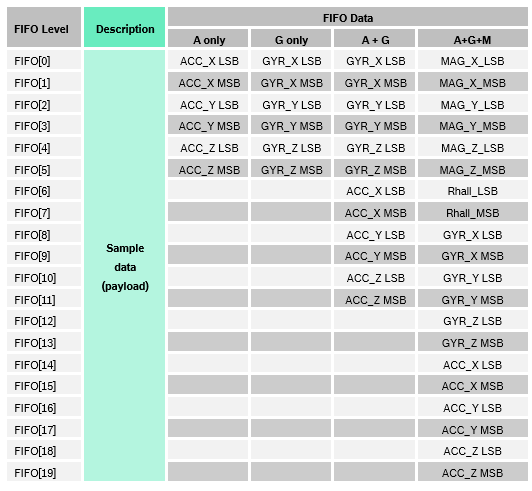

When the FIFO is set to headerless mode, only sensor data is stored in the FIFO (in the same order as in the data register). Any combination of accelerometer, gyroscope and external sensor data can be stored. External interrupt tags are not supported in headerless mode. After the configuration is complete, the frame size in headerless mode is constant.

The data stored in the FIFO uses the following formats in headerless mode:

Table 5: FIFO data formats in headerless mode

Note:

When overread occurs, a byte stream of 0x0080 (which corresponds to (LSB, MSB) byte order to a data value of 0x8000) is returned in headerless mode.

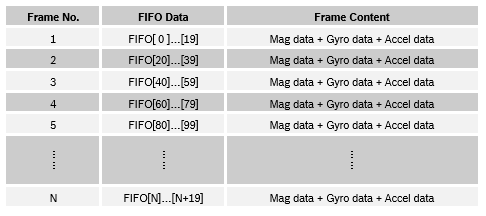

Example: How data stores in FIFO in Headerless mode

- Write 0x11, 0x15 to CMD register 0x7E in sequence to set A, G to normal power mode.

- Write 0x28 to register ACC_CONF (0x40) to set the acceleration data rate to 100Hz.

- Write 0x28 to register GYR_CONF (0x42) to set the gyro data rate to 100Hz.

- Enable and configure M via the secondary interface according to the application note “BMI160 Secondary Interface: Magnetometer”, and set the magnetic data rate to 100Hz.

- Write 0xE0 into register FIFO_CONFIG_1 (0x47) to enable A, G and M data stored in FIFO, and disable the header and timestamp for the FIFO.

Then the FIFO works and stores data in the following format:

Table 6: FIFO data in headerless mode

Note:

In Headerless mode, the output data rates of all enabled sensors for the FIFO should be identical. If the output data rates are different, the FIFO will wait until the data with the lowest output data rate is ready and then store the frame as described in Section 3.1.3.

Retrieving data from FIFO

Communication speed and FIFO fill rate

The communication speed determines the rate at which data can be read from the FIFO. To prevent data loss, fill the FIFO with a rate that does not exceed the read rate. The appropriate appropriate data rate of each sensor should be selected.

For I2C protocol, a read sequence consists of a one-byte I2C write phase followed by the I2C read phase. Using the formula (1) in Section 4.1, the average frame size is approximately 13 bytes when Aodr, Godr and Modr are 1600Hz, 1600Hz and 25 Hz correspondingly. The minimum time necessary for starting the burst read for I2C fast mode is roughly 75 µs. The minimum time to get the above-mentioned frame is roughly 360 µs, including all minimum start and stop setup and hold times and minimum cycle period. As a result, data can still be read out of the FIFO faster than it is put into the FIFO at the data rate of 1600 Hz, corresponding to a period of 625 µs.

However, the theoretical maximum FIFO fill rate for the BMI160 FIFO can be calculated as follows:

fFIFO_fill = Max(Aodr,Godr,Modr) * Frame_SizeAVG

= Max(Aodr,Godr,Modr) * 1+ 6 * Aodr + 6 * Godr + 8 * Modr (2)

= 6400 + 6 * 1600 + 6 * 6400 + 8 * 800

= 60800 (bytes/second) = 486.4 kbit/s

In this case, the maximum FIFO fill rate exceeds the speed of I2C fast mode. The data rates of the sensors can be adjusted for the I2C communication speed. On the other hand, SPI with higher speed can be used to meet the high FIFO fill rate requirement when all the sensors are with high output data rates.

Watermark

The watermark interrupt is triggered when the FIFO fill level in fifo_byte_counter in FIFO Length Registers (0x22-0x23) is above a pre-configured fifo_watermark in FIFO Configuration Registers (0x46-0x47) and it remains set until the condition causing it is eliminated. To clear the watermark interrupt, read the FIFO until the fill level in fifo_byte_counter is lower than the value stored in fifo_watermark; however, reading more than the valid frames in FIFO is recommended for two reasons:

- It prevents the watermark interrupt from being triggered too often, without compromising the benefit of using FIFO.

- A Sensortime frame is returned after the last valid frame when more data than valid frames in FIFO are read.

FIFO operation with watermark interrupt

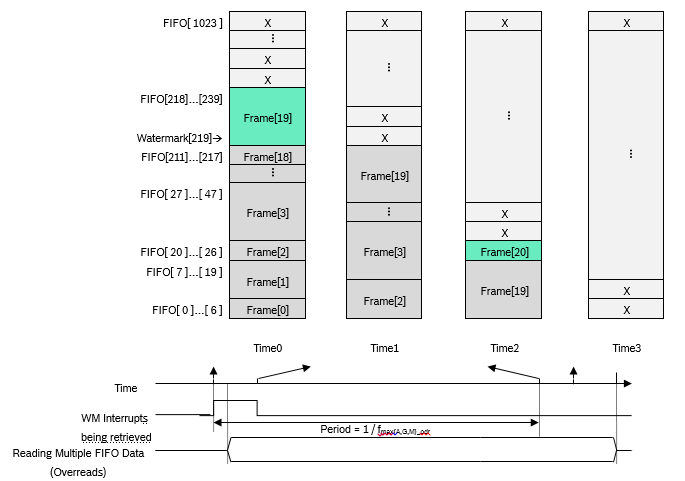

The example in Figure 6 shows how the FIFO operates with watermark interrupt. The pre-configured watermark is 220 bytes so that the unit of fifo_watermark is 4 bytes and is configured as 0x37. At Time0, the FIFO fill level in fifo_byte_counter is 218 bytes. At Time1, the FIFO fill level is updated to 239 bytes when Frame[19] is pushed into the FIFO. Then the FIFO watermark interrupt is fired. After some latency, the interrupt is serviced and a burst read that reads all the frames in the FIFO is issued. At Time2, the complete frame Frame[0] is read, fifo_byte_counter is updated but still above the watermark, so the FIFO watermark interrupt remains set. Until another complete frame Frame[1] is read at Time3, the updated fifo_byte_counter is below the watermark and the watermark interrupt is cleared.

Figure 6: Watermark Interrupt is cleared when FIFO Counter is below pre-configured watermark

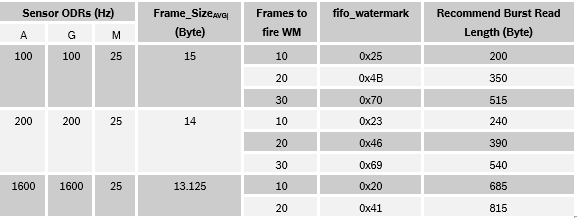

Watermark level and burst read length

The watermark level (WM) can be calculated with the number of frames (F) that triggers a watermark interrupt:

WM = F * Frame_SizeAVG / 4 (3)

= F * (0.25+1.5*Aodr/ Max(Aodr,Godr,Modr) +1.5*Godr/ Max(Aodr,Godr,Modr) +2*Modr/ Max(Aodr,Godr,Modr))

In order to read more data than the valid frames in FIFO, the minimum Burst Read Length can be roughly estimated with the calculated watermark level, FIFO fill rate, communication speed (Clock Rate), and the latency of serving watermark interrupt:

Read_Lengthmin = (WM*4 + fFIFO_fill * Latencyfwm_int) / (1 – fFIFO_fill / fCLK) (4)

If I2C Fast mode is used and the maximum latency of serving watermark interrupt is 10 ms, the recommended burst read lengths for different sensor and watermark configurations are provided in Table 8.

Table 7: WM configuration and burst read length for different ORDs (I2C fast mode)

Note:

New frames can be filled into FIFO during the latency for interrupt service and a long burst read. A high watermark level is not recommended if the sensors are set to high ODRs and the communication speed is not fast enough.

Potential risk and possible solution

There is a potential risk that watermark is triggered again shortly after it is cleared while the FIFO data is still being read. This may unintentionally call a false watermark interrupt service before the current watermark interrupt service is finished, and thus lead to a system crash. For the same communication speed, the higher the FIFO fill rate, the more likely the potential risk occurs. The risk is illustrated in Figure 7. At Time2, fifo_byte_counter is below the watermark level so the interrupt is cleared. However, at Time3, before the oldest frame Frame[2] is completely read out, the new frame Frame[20] is pushed into FIFO and an unwanted interrupt is triggered.

Figure 7: Watermark Interrupt is triggered immediately after it is cleared

One possible solution is to disable the watermark interrupt by setting bit 6 to ‘0’ in Register (0x51) INT_EN_1 at the beginning of the interrupt service and enable the watermark interrupt again before exiting the interrupt service.

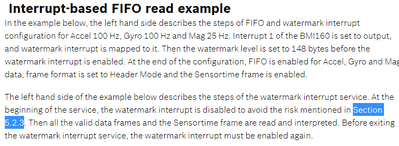

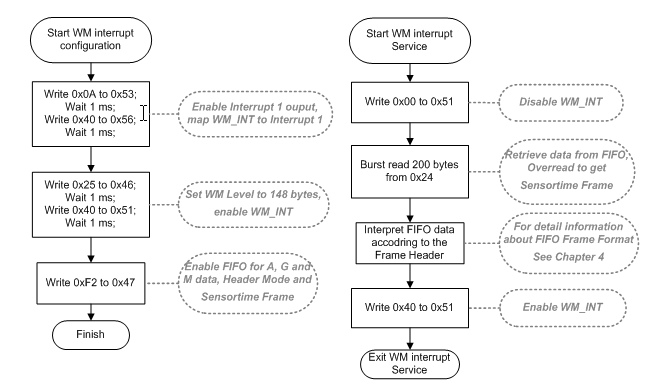

Interrupt-based FIFO read example

In the example below, the left hand side describes the steps of FIFO and watermark interrupt configuration for Accel 100 Hz, Gyro 100 Hz and Mag 25 Hz. Interrupt 1 of the BMI160 is set to output, and watermark interrupt is mapped to it. Then the watermark level is set to 148 bytes before the watermark interrupt is enabled. At the end of the configuration, FIFO is enabled for Accel, Gyro and Mag data, frame format is set to Header Mode and the Sensortime frame is enabled.

The left hand side of the example below describes the steps of the watermark interrupt service. At the beginning of the service, the watermark interrupt is disabled to avoid the risk mentioned in Section 5.2.3. Then all the valid data frames and the Sensortime frame are read and interpreted. Before exiting the watermark interrupt service, the watermark interrupt must be enabled again.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

very detailed, thanks

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

To which referenced chapters or sections are you referring?

An example:

Is there other documentation rather than this application note and the datasheet?

Thanks

Still looking for something?

- Top Results